| CISC and RISC p              | processors                   |

|------------------------------|------------------------------|

| CISC                         | RISC                         |

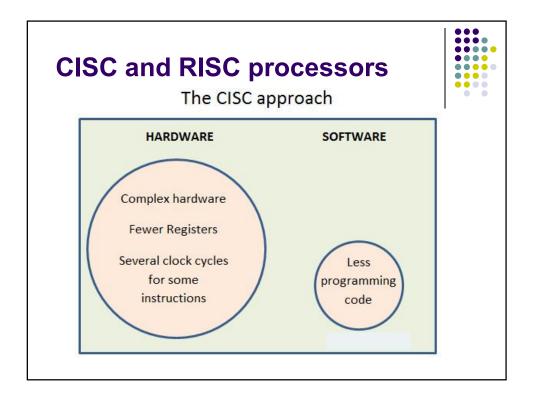

| Emphasis on hardware         | Emphasis on software         |

| Includes multi-clock         | Single-clock,                |

| complex instructions         | reduced instruction only     |

| Memory-to-memory:            | Register to register:        |

| "LOAD" and "STORE"           | "LOAD" and "STORE"           |

| incorporated in instructions | are independent instructions |

| Small code sizes,            | Low cycles per second,       |

| high cycles per second       | large code sizes             |

| Transistors used for storing | Spends more transistors      |

| complex instructions         | on memory registers          |

| CISC and RISC                                            | processors                                   |   |  |

|----------------------------------------------------------|----------------------------------------------|---|--|

| RISC                                                     | CISC                                         |   |  |

| Fewer instructions                                       | More instructions                            |   |  |

| Simpler instructions                                     | More complex instructions                    |   |  |

| Small number of instruction formats                      | Many instruction formats                     |   |  |

| Single-cycle instructions whenever possible              | Multi-cycle instructions                     |   |  |

| Fixed-length instructions                                | Variable-length instructions                 |   |  |

| Only load and store<br>instructions to address<br>memory | Many types of instructions to address memory | ) |  |

| Fewer addressing modes                                   | More addressing modes                        |   |  |

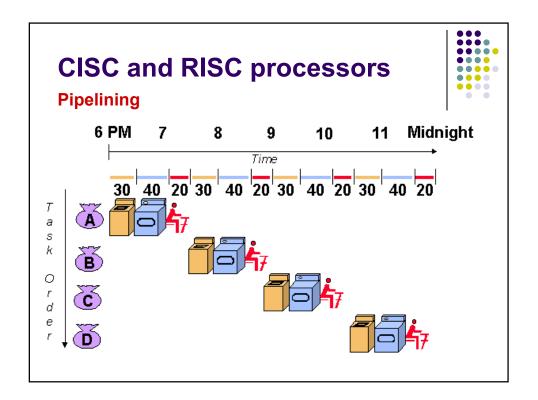

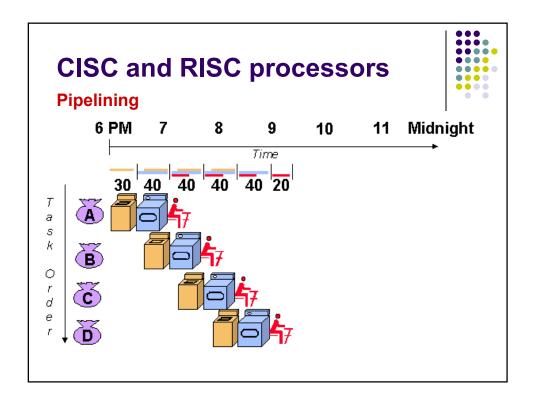

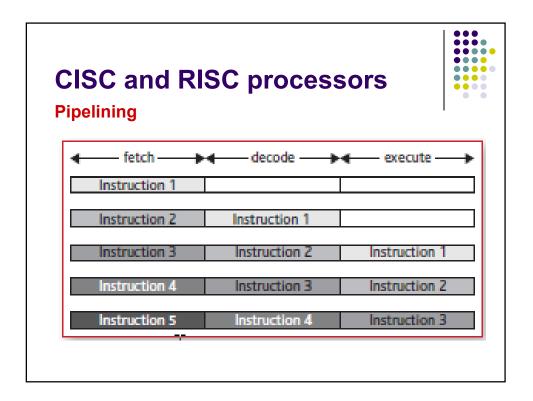

| CISC a<br>Pipelining |       |       | -     |      |         |     |              |     |   |

|----------------------|-------|-------|-------|------|---------|-----|--------------|-----|---|

| > instructio         |       | •     | ,     | 、    |         |     |              |     |   |

| instruction          |       |       | ``    | )    |         |     |              |     | I |

| operand              |       | ``    | ,     | • 、  |         |     |              |     |   |

| instruction          |       |       | ``    | ,    |         |     |              |     |   |

| result wr            | ite d | аск ( | (VVB) |      | ck cycl | es  |              |     |   |

|                      |       | 1     | 2     | 3    | 4       | 5   | 6            | 7   |   |

|                      | IF    | 1.1   | 2.1   | 3.1  | 4.1     | 5.1 | 6.1          | 7.1 |   |

| nits                 | ID    |       | 1.2   | 2.2  | 3.2     | 4.2 | 5.2          | 6.2 |   |

|                      | OF    |       |       | 1.3  | 2.3     | 3.3 | 4.3          | 5.3 |   |

| ssor u               |       |       |       |      | 1.4     | 2.4 | 3.4          | 4.4 |   |

| Processor units      | IE    | 1000  |       | 1272 | 1.4     | 2.4 | I NEEDE TO A |     |   |